1 - سطح گیت

جلسه اول (ماژول ها) جلسه دوم (گیت ها) جلسه سوم (نوع سیگنال) جلسه چهارم (پایان فصل)2 - مقداردهی مداوم

جلسه پنجم (اُپراتور ها) جلسه ششم (آرایه ها) جلسه هفتم (شرط ها) جلسه هشتم (فراخوانی ماژول) جلسه نهم (تست بنچ) جلسه دهم (نگاشت حافظه)3 - سطح رفتاری (ترکیبی)

جلسه یازدهم (بلاک Always) جلسه دوازدهم (ابزار ها) جلسه سیزدهم (نوع پردازش) جلسه چهاردهم (نکات تکمیلی) جلسه پانزدهم (پایان فصل)4 - سطح رفتاری (ترتیبی)

جلسه شانزدهم (لبه ها) جلسه هفدهم (تست بنچ 2) جلسه هجدهم (شمارنده ها) جلسه نوزدهم (ضرب و شیفت) جلسه بیستم (استیت ماشین) جلسه بیست و یکم (کشف رشته) جلسه بیست و دوم (فرکانس) جلسه بیست و سوم (نان بلاک) جلسه بیست و چهارم (پایان)5 - جلسات تمرینی

جلسه تمرین اول (تاخیر ها) جلسه تمرین دوم (الحاق-منطق) جلسه تمرین سوم (شیفت ها) جلسه تمرین چهارم (استیت)6 - مثال های پروژه محور

پروژه طراحی پردازنده RTL پروژه پردازنده Maano پروژه پردازنده MIPS7 - ارتباط و گفتگو

ارتباط با نویسنده گروه تلگرام تبلیغات و آگهیآموزش وریلاگ - جلسه 11 :

آموزش وریلاگ آموزش Verilog

در این جلسه میخوایم با یک ساختار جدید به نام always آشنا بشیم که در این ساختار میشه از اُپراتور های جبری استفاده کرد ، اما سوال اینجاست : مگه نمیشد این اُپراتور ها رو در ساختار assign به کار گرفت ؟ پس چرا اومدیم سراغ یک ساختار جدید ؟ دو دلیل داره ، اول اینکه ما درون ساختار های always می تونیم از ابزار هایی مثل if های تودرتو ، case و ... استفاده کنیم که باعث میشن حجم کدهای ما کمتر بشن . ثانیا برای پیاده سازی مدارات ترتیبی (یا همون مداراتی که با لبه کلاک کار میکنند) به ساختاری نیاز دارید که بهش بگید هر وقت لبه کلاک اومد محاسبات انجام بشه . آیا در assign چنین چیزی داشتیم ؟ خیر ، اما در فصل چهارم شاهد پیاده سازی چنین مداراتی خواهیم بود که با لبه کلاک کار خواهند کرد . در این فصل قصد داریم با مداراتی آشنا بشیم که به کمک ابزار های مختلف در ساختار always پیاده سازی می شوند و به اصطلاح مدارات فاقد کلاک یا ترکیبی هستند .

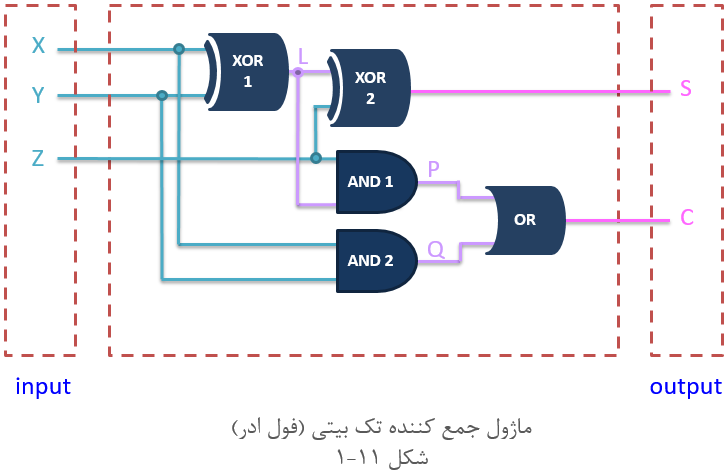

فرض کنید قراره ماژول جمع کننده تک بیتی بالا رو با استفاده از عبارت های جبری در بلاک always پیاده سازی کنیم . اگه یادتون باشه جلسات اول گفته بودیم که تمامی سیگنال هایی که در always مقدار دهی می شوند باید از نوع reg تعریف شوند . بنابراین هرچیزی که توی این بلاک دیدید که سمت چپ علامت = بود رو باید reg تعریف کنید . مابقی سیگنال ها کاملا سلیقه ای هست ، می تونن reg باشن و یا wire باشند . البته سیگنال هایی که ورودی اصلی ماژول هستن حق ندارند reg تعریف شوند .

1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12- 13- 14- 15- 16- 17- 18- 19- 20-

module FullAdder( input X, input Y, input Z, output reg S, output reg C ); reg L,P,Q; always @(X or Y or Z) // always @(*) begin L = X ^ Y; P = L & Z; Q = X & Y; S = L ^ Z; C = P | Q; end endmodule

تمامی خط هایی که قراره توی بلاک always اجرا بشن رو باید بین begin و end قرار بدیم . به نوعی اینجوری مشخص میکنیم ابتدا و انتهای بلاک always کجاست . البته یک تبصره وجود داره ، اگه توی بلاک always فقط یک خط برنامه نوشتید ، می تونید این begin و end رو نذارید ولی بهتره که بذارید ، چرا ؟ چون ممکنه بعدا به برنامه خودتون مراجعه کنید و بخواین یه سری خطوط درون بلاک اضافه کنید. این قضیه begin و end توی تعریف if و case هم صادقه که وقتی بهشون رسیدیم مجددا توضیح میدم . خط 11 رو ببینید ، جلوی کلمه always نوشتیم @(X or Y or Z) این چیه ؟ به این میگن لیست حساسیتِ بلاک ، معمولا توی این لیست باید ورودی های مدار رو بنویسیم ، البته یه راه میانبر وجود داره که از شر این لیست خلاص بشیم ، فقط کافیه توی این لیست علامت ستاره رو بذاریم تا بصورت اتوماتیک لیست حساسیت توسط خود وریلاگ محاسبه بشه . بنابراین میشه نوشت @(*) و ما از این به بعد همین کار رو خواهیم کرد . حالا بیاین بجای استفاده از اُپراتور های منطقی ، این جمع کننده رو با اُپراتور های جبری پیاده سازی کنیم :

1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12- 13- 14- 15-

module FullAdder( input X, input Y, input Z, output reg S, output reg C ); always @(*) begin {C,S} = X + Y + Z; end endmodule

همونطور که میبینید چون داریم رفتار ماژول رو توصیف میکنیم به سیگنال های واسطه ای احتیاجی نبود و تعریف شون نکردیم . فقط خروجی های مدار رو reg قرار دادیم . گذاشتن begin و end الزامی نبود چرا که فقط یک خط برنامه در این بلاک نوشته شده ، اما حرفه ای تر عمل کردیم و گذاشتیم . همچنین لیست حساسیت را طبق قرارمون با استفاده از ستاره تکمیل کردیم . در این مثال من می تونستم خروجی رو S دو بیتی تعریف کنم و مقدار جمع رو توی S بریزم اما کاملا سلیقه ای و دلبخواهی ، مقدار جمع رو توی دو سیگنال S و C که تک بیتی هستند ریختم و بدین منظور از الحاق استفاده کردم . اگه الحاق رو یادتون رفته چیه ، به جلسه تمرین دوم مراجعه کنید . دانلود فیلم جلسه

رفتن به جلسه بعد ...

پویا

سلام استاد وقتتون بخیر ببخشید فرمودین 32 هزار تومان نه دو میلیون و خورده ای !

سید محسن

سلام ، موقتی هست و هفته بعدی برمیگرده به حالت قبل .

مرتضی

ببخشید در ویدیو گفتید قیمت دوره 32 هزار تومان هست ولی چک کردم 340 تومن بود؟

سید محسن

سلام ، قیمت نسبت به سه سال پیش بروزرسانی شد و پرداخت داوطلبانه هم حذف شد .