1 - سطح گیت

جلسه اول (ماژول ها) جلسه دوم (گیت ها) جلسه سوم (نوع سیگنال) جلسه چهارم (پایان فصل)2 - مقداردهی مداوم

جلسه پنجم (اُپراتور ها) جلسه ششم (آرایه ها) جلسه هفتم (شرط ها) جلسه هشتم (فراخوانی ماژول) جلسه نهم (تست بنچ) جلسه دهم (نگاشت حافظه)3 - سطح رفتاری (ترکیبی)

جلسه یازدهم (بلاک Always) جلسه دوازدهم (ابزار ها) جلسه سیزدهم (نوع پردازش) جلسه چهاردهم (نکات تکمیلی) جلسه پانزدهم (پایان فصل)4 - سطح رفتاری (ترتیبی)

جلسه شانزدهم (لبه ها) جلسه هفدهم (تست بنچ 2) جلسه هجدهم (شمارنده ها) جلسه نوزدهم (ضرب و شیفت) جلسه بیستم (استیت ماشین) جلسه بیست و یکم (کشف رشته) جلسه بیست و دوم (فرکانس) جلسه بیست و سوم (نان بلاک) جلسه بیست و چهارم (پایان)5 - جلسات تمرینی

جلسه تمرین اول (تاخیر ها) جلسه تمرین دوم (الحاق-منطق) جلسه تمرین سوم (شیفت ها) جلسه تمرین چهارم (استیت)6 - مثال های پروژه محور

پروژه طراحی پردازنده RTL پروژه پردازنده Maano پروژه پردازنده MIPS7 - ارتباط و گفتگو

ارتباط با نویسنده گروه تلگرام تبلیغات و آگهیآموزش وریلاگ - جلسه 17 :

آموزش وریلاگ آموزش Verilog

این جلسه در مورد تست بنچ مدارات ترتیبی هستش که البته برای دوستانی که با ویدئو همراه ما هستن اجباری نیست ، چون ما توی ویدئو هامون هر ماژولی که می نویسیم سریعا تست بنچ و شکل موج خروجی شو هم باهم کار میکنیم .

1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12- 13- 14- 15- 16- 17- 18- 19-

module DFF( input Clk, input Rst, input D, output reg Q, output Qp ); assign Qp=~Q; always @(posedge Clk or negedge Rst) begin if (Rst==0) Q=0; else Q=D; end endmodule

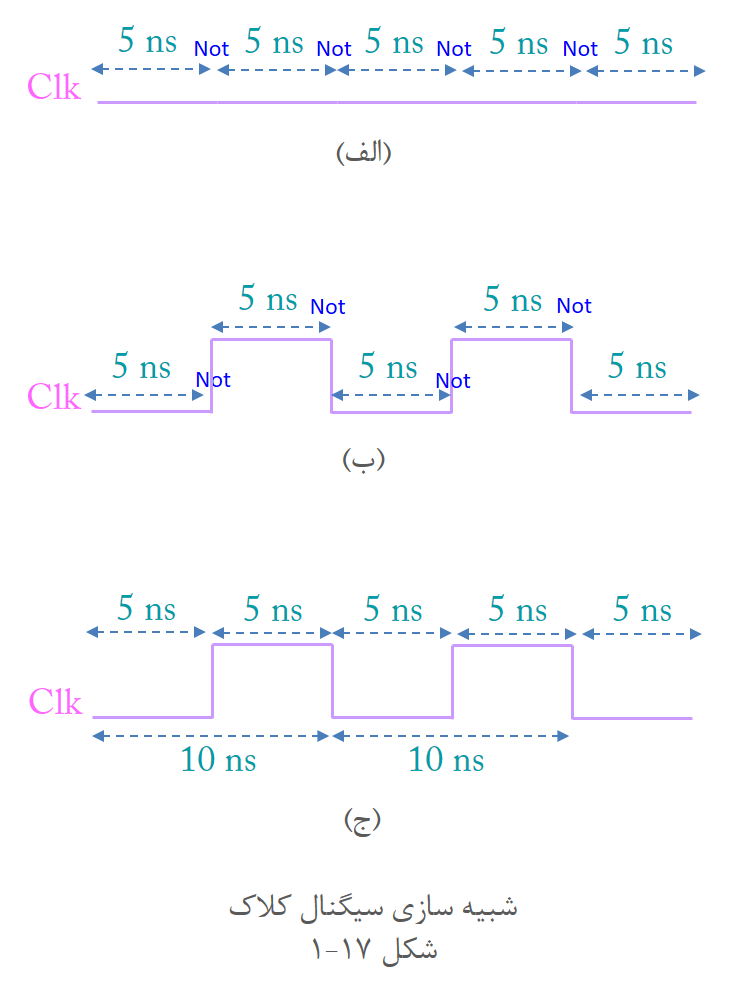

فرض کنید برای فلیپ فلاپ D کد بالا میخوایم تست بنچ بنویسیم ، تست بنچ مدارات ترتیبی از نظر ساختار مشابه مدارات ترکیبی هست (جلسه 9) ، ورودی مدارات ترتیبی معمولا کلاک و ریست هست و حالا اگه ورودی های دیگه هم باشه که خب اضافه میکنیم . تنها تفاوت تست بنچ نویسی مدارات ترکیبی و ترتیبی سر همین کلاک هست . کلاک رو چطور به عنوان ورودی توی تست بنچ مقداردهی کنیم ؟ ببینید ورودی کلاک چیز خاصی نیست اونهم مثل بقیه ورودی ها یه سیم یا سیگنال هست ، با این تفاوت که مُدام بالا پایین میشه . شکل الف زیر رو ببینید یه سیم داریم که مقدارش 0 هست . فرض کنید ما هر 5 نانوثانیه مقدار این سیم رو نات کنیم . چه اتفاقی میفته ؟

همونطور که توی شکل ب میبینیم ، نات کردن در هر 5 نانوثانیه باعث میشه سیم ما هر 5 نانوثانیه مقدار صفر یا یک رو به خودش بگیره و در شکل ج مشخص میشه که وقتی هر 5 نانوثانیه این کار رو کنیم ، دوره تناوب کلاک ما 10 نانوثانیه خواهد بود. خب به همین راحتی ما از یه سیم ساده یه کلاک با دوره تناوب 10 نانو ثانیه ساختیم . اما کد وریلاگ اون چطور میشه :

1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12- 13- 14- 15- 16- 17- 18- 19- 20- 21- 22- 23- 24- 25- 26- 27- 28- 29-

module TestBench_DFF; reg Clk,Rst,D; wire Q,Qp; DFF U (.Clk(Clk), .Rst(Rst), .D(D), .Q(Q), .Qp(Qp)); initial begin Clk=0; D=1; Rst=0; #100; Rst=1; #60; D=0; #60; D=1; #60; Rst=0; end always #5 Clk=~Clk; endmodule

مجددا مرور کنیم ، توی خط 1 یه اسم دلخواه برای ماژول تست بنچ انتخاب میکنیم . این ماژول نه ورودی داره و نه خروجی . حالا توی خطوط بعدی به ازای ورودی های ماژولی که واسش تست بنچ میخایم بنویسیم reg تعریف میکنیم و به ازای خروجی های اون ماژول wire تعریف میکنیم . حالا توی خط 6 عمل فراخوانی رو انجام میدیم . اسم ماژول اصلی رو که DFF بود مینویسیم و یه اسم مستعار مثلا U واسش انتخاب میکنیم . حالا مطابق خط 6 تا 10 ورودی و خروجی هارو بهم وصل میکنیم . بعدش توی خط 12 از یه بلاک initial استفاده میکنیم تا مقادیر ورودی هارو مشخص کنیم . معمولا اینجا ابتدا کلاک رو صفر میکنیم و بعد دیگه بهش دست نمیزنیم . برای ریست هم معمولا ابتدا فعالش میکنیم (ریست رو مساوی صفر قرار میدیم) و بعد از چند نانوثانیه غیر فعالش میکنیم (ریست رو مساوی یک قرار میدیم) ، بدین ترتیب من به ازای 100 نانوثانیه مدار رو ریست کردم و گفتم بعد از 100 نانوثانیه مدار از ریست در بیاد و شروع کنه به کار کردن . حالا ورودی های دیگه ای اگه دارم مقداردهی شون میکنم که توی فلیپ فلاپ D فقط یه ورودی به اسم D داریم که من کاملا دلبخواهی مقادیر مختلف رو توی خط 20 تا 23 بهش دادم . توی خط 24 هم مجددا ریست رو فعال کردم تا مدار ریست بشه (چرا ؟ دوست داشتم ، دلبخواهی ، شما میخای خط 24 رو ننویس و مدار تو ریست نکن). حالا نوبت به مقداردهی کلاک میرسه ، ما توی initial فقط در لحظه اول کلاک رو صفر کردیم ، حالا باید کلاک رو نات کنیم و بسازیم . خارج از بلاک initial توی یه بلاک always میگیم کلاک مساوی بشه با نات کلاک البته با 5 نانو ثانیه تاخیر، این باعث میشه هر 5 نانوثانیه سیم کلاک مقدارش نات بشه دقیقا مشابه شکل 17-1 و دوره تناوب کلاک هم 10 نانوثانیه خواهد بود ، به همین راحتی . دانلود فیلم جلسه

رفتن به جلسه بعد ...

آوا مهجوری

سلام تست بنچ ارور میده.نفهمیدم مشکلش چیه

سید محسن

سلام ، من مجددا کد رو بررسی کردم توی نرم افزار ، دقیقا همینارو کپی کردم هیچ مشکلی نبود ، ایراد سینتکس و خطای سینتکس نداشت ، از نظر اجرا هم ، اجرا شد و خروجی گرفتم . با دقت بیشتری بررسی کنید

حسین

تایم اسکیل رو نباید بنویسیم که نانو ثانیه هست یا پیکو ثانیه ؟

سید محسن

سلام به صورت دیفالت نانو ثانیه در نظر میگیره ولی بله بهتره که بذاریم ، پس توی خط اول تست بنچ این رو اضافه کنید `timescale 1ns / 1ps

علی

سلام من یه خراب کاری کردم در بین سیمولیشن گرفتن به دلیل این که سیمولیشن خراب شده بود از تسک منیجر از مدل سیم خارج شدم حالا هر چی دوباره وارد می شم هیچ کدوم از ماژولا رو سیو نمی کنه و کامپایل هم نمی کنه فقط یه با یه پیغام داد که برای کامپایل یه فایلی رو نمی تونم پیدا کنم خیلی کارم گیره می تونید یه راهنمایی کنید ؟

سید محسن

سلام ، نرم افزار مدلسیم این مشکلات غیرمنطقی واسش پیش میاد معمولا . سعی کنیم پروژه رو از اول بسازید و تمام مراحل ساخت رو مجددا طی کنید .

anonymous

درود بر سید محسن

سید محسن

درود بر خودت :)