1 - سطح گیت

جلسه اول (ماژول ها) جلسه دوم (گیت ها) جلسه سوم (نوع سیگنال) جلسه چهارم (پایان فصل)2 - مقداردهی مداوم

جلسه پنجم (اُپراتور ها) جلسه ششم (آرایه ها) جلسه هفتم (شرط ها) جلسه هشتم (فراخوانی ماژول) جلسه نهم (تست بنچ) جلسه دهم (نگاشت حافظه)3 - سطح رفتاری (ترکیبی)

جلسه یازدهم (بلاک Always) جلسه دوازدهم (ابزار ها) جلسه سیزدهم (نوع پردازش) جلسه چهاردهم (نکات تکمیلی) جلسه پانزدهم (پایان فصل)4 - سطح رفتاری (ترتیبی)

جلسه شانزدهم (لبه ها) جلسه هفدهم (تست بنچ 2) جلسه هجدهم (شمارنده ها) جلسه نوزدهم (ضرب و شیفت) جلسه بیستم (استیت ماشین) جلسه بیست و یکم (کشف رشته) جلسه بیست و دوم (فرکانس) جلسه بیست و سوم (نان بلاک) جلسه بیست و چهارم (پایان)5 - جلسات تمرینی

جلسه تمرین اول (تاخیر ها) جلسه تمرین دوم (الحاق-منطق) جلسه تمرین سوم (شیفت ها) جلسه تمرین چهارم (استیت)6 - مثال های پروژه محور

پروژه طراحی پردازنده RTL پروژه پردازنده Maano پروژه پردازنده MIPS7 - ارتباط و گفتگو

ارتباط با نویسنده گروه تلگرام تبلیغات و آگهیآموزش وریلاگ - تمرین 1 :

آموزش وریلاگ آموزش Verilog

میخایم درباره تاخیر ها صحبت کنیم . ببینید تاخیر ها معمولا توی وریلاگ استفاده نمیشن چون ما هیچوقت نمی تونیم تعیین کنیم واقعا گیت ها و قطعات دیجیتال در دنیای واقعی ، چقد تاخیر دارن ولی خب بعضی مواقع دوست داریم بدونیم اگه تاخیر قطعات فلان قدر باشه ، مدار چطور عمل میکنه . این جلسه به تاخیر خروجی گیت ها میپردازیم ، که اگه یه گیت داشته باشیم ، به خروجی گیت چه تاخیر هایی میتونیم اعمال کنیم .

به تصویر بالا نگاه کنید ، خروجی یه گیت and بدون تاخیر هستش ، ما نمیدونیم خروجی گیت 0 هست یا 1 هست چون از ورودی گیت بی اطلاعیم ، اما اگه خروجی بخواد از 0 به 1 بره یا از 1 به 0 بره ، بدون تاخیر و بصورت آنی یهو میره .

1- 2- 3- 4- 5- 6- 7- 8- 9-

module Gate_Delay( input A, input B, output F ); and (F,A,B); endmodule

اینم کد وریلاگ این گیت که میبینید خبری از تاخیر نیست .

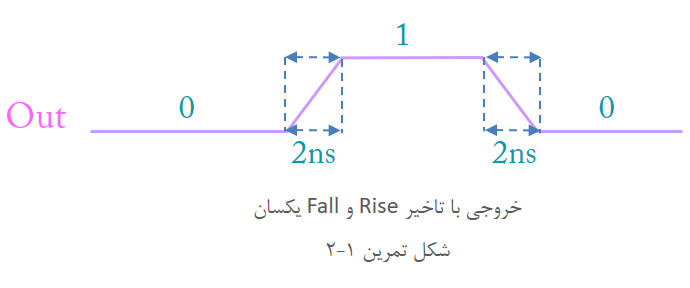

حالا شکل بالا رو نگاه کنید ، باز هم خروجی یه گیت and هست و ما نمیدونیم خروجی این گیت 0 هست یا 1 هست اما بخوبی میبینیم که اگه بخواد از 0 به 1 بره و یا از 1 به 0 بره ، با 2 نانو ثانیه تاخیر این کار رو انجام میده . یعنی وقتی خروجی گیت میخواد از 0 به 1 بره ، به مدت 2 نانوثانیه خروجی همچنان 0 می مونه و بعدش به 1 میره . همینطور توی قسمت دوم وقتی خروجی قراره از 1 به 0 بره ، به مدت 2 نانوثانیه اضافه تر مقدار 1 رو نگه میداره و سپس 0 میشه .

1- 2- 3- 4- 5- 6- 7- 8- 9-

module Gate_Delay( input A, input B, output F ); and #(2) (F,A,B); endmodule

کد وریلاگ بالا داره میگه اگه خروجی گیت ما ، خواست از 0 به 1 بره یا بالعکس ، این کار رو با 2 نانوثانیه تاخیر انجام بده . مثلا اگه توی نانوثانیه 156 خروجی ما 0 هست و یهو ورودی ها عوض شدن (1 و 1 شدن) وخروجی گیت ما خواست 1 بشه ، توی نانوثانیه 156 یک نمیشه ، بلکه خروجی همچنان صفر باقی می مونه تا نانوثانیه 158 و سپس توی نانوثانیه 158 ، یک میشه .

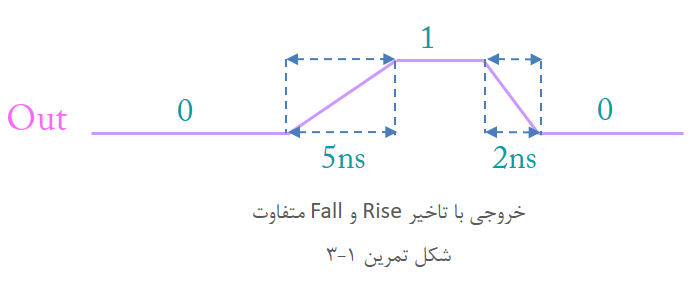

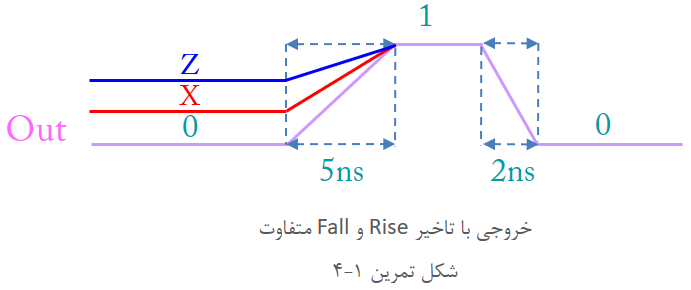

تاخیر هارو میشه از هم تفکیک کرد ، تاخیر رایس یعنی وقتی خروجی ما قراره از یه مقداری به 1 بره و تاخیر فال یعنی وقتی خروجی ما قراره از یه مقداری به 0 بره . توی تصویر بالا تاخیر رایس 5 نانوثانیه و تاخیر فال 2 نانوثانیه در نظر گرفته شده که باید کد وریلاگ شو بنویسیم .

1- 2- 3- 4- 5- 6- 7- 8- 9-

module Gate_Delay( input A, input B, output F ); and #(5,2) (F,A,B); endmodule

عدد اول تاخیر رایس و عدد دوم تاخیر فال رو تعیین میکنه . بنابراین اگه خروجی 0 بود و خواست 1 بشه ، به مدت 5 نانوثانیه اضافه تر 0 باقی می مونه و سپس 1 میشه . همچنین اگه 1 بود و خواست 0 بشه ، به مدت 2 نانوثانیه اضافه تر 1 باقی می مونه و سپس صفر میشه .

به این نکته دقت کنید ، ما وقتی میگیم تاخیر رایس یعنی میزان تاخیری که خروجی از مقداری به مقدار 1 برسه ، منظورمون تنها از 0 به 1 نیست . بلکه اگه خروجی ما 0 ، X یا Z بود و خواست به 1 بره ، به مدت 5 نانوثانیه مقدار 0 ، X یا Z خودش رو حفظ میکنه و سپس 1 میشه . برای تاخیر فال هم به همین صورت ، مهم نیست خروجی مقدارش 1 هست یا Z و یا X ، اگه خروجی خواست صفر بشه به مدت 2 نانوثانیه خروجی مقدار 1 یا X یا Z رو حفظ میکنه و سپس 0 میشه.

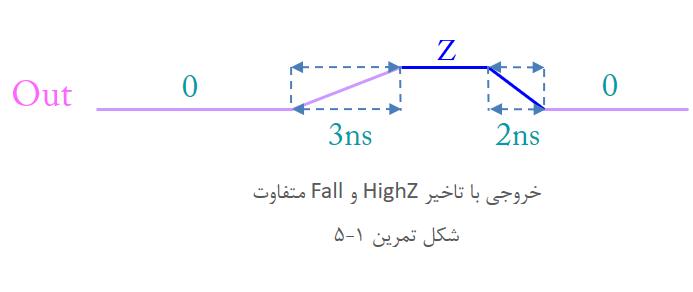

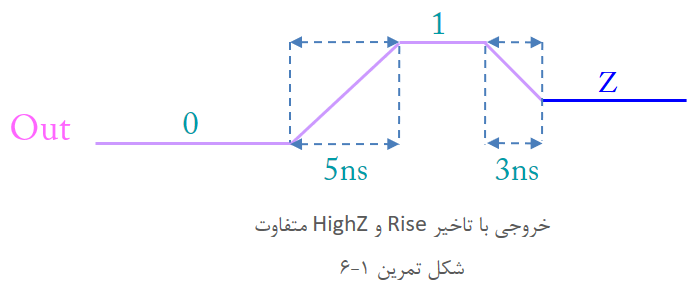

خب ما تا اینجا مشخص کردیم وقتی خروجی خواست 0 بشه یا خواست 1 بشه ، چه تاخیری داشته باشه . حالا اگه خروجی خواست Z بشه چطور ؟ شکل بالا میگه خروجی اگه خواست Z بشه با 3 نانوثانیه تاخیر انجام بشه که بهش میگیم تاخیر TurnOff و اگه خواست 0 بشه با 2 نانوثانیه تاخیر انجام بشه که همون تاخیر Fall هست ، تاخیر Rise رو مشخص نکرده که خودمون 5 نانوثانیه در نظر میگیریم.

1- 2- 3- 4- 5- 6- 7- 8- 9-

module Gate_Delay( input A, input B, output F ); and #(5,2,3) (F,A,B); endmodule

در کد بالا عدد اول تاخیر Rise ، عدد دوم تاخیر Fall و عدد سوم تاخیر TurnOff رو تعیین میکنه . برای همون شکل بالا وقتی خروجی 0 هست ، بخواد Z بشه به مدت 3 نانوثانیه صفر باقی می مونه و سپس Z میشه و وقتی خواست از Z به 0 بره ، به مدت 2 نانوثانیه اضافه تر Z باقی می مونه و سپس صفر میشه .

برای شکل بالا نیازی نیست کد جدید بنویسیم ، همون کد وریلاگ قبلی که نوشتیم همین کار رو میکنه ، اگه خروجی بخواد 1 بشه با 5 نانوثانیه تاخیر 1 میشه که همون تاخیر Rise ماست و وقتی هم که میخواد Z بشه با 3 نانوثانیه تاخیر Z میشه که همون تاخیر TurnOff ماست . البته معمولا توی درس و امتحان های تئوری بما شکل رو نمیدن که بگن کد وریلاگ تاخیر شو بنویس ، بلکه کد وریلاگ تاخیر رو میدن و بما میگن شکل موج خروجی رو رسم کن که ما باید ببینیم ورودی ها چه زمانی تغییر میکنند ، سپس مشخص کنیم در اون زمانها خروجی قراره به چه مقداری بره ؟ 0 یا 1 یا Z ؟ و مقدار جدید خروجی رو با تاخیر مربوطه رسم کنیم . پس توی تاخیر ها تقریبا سه نکته مهمه ، الف) ورودی ها چه زمانی تغییر میکنند ؟ و آیا باعث تغییر خروجی می شوند یا خیر ؟ ب) خروجی ما قرار است به چه مقدار جدیدی برود ؟ ج) درطول تاخیر ، خروجی مقدار قبلی خود را حفظ میکند و سپس به مقدار جدید میرود. حالا به کد زیر نگاه کنید ، یک نوع تاخیر دیگه هم داریم که هنگام محاسبات اعمال میشه ، کد زیر میگه هرگاه مقدار A و B عوض شد و خواستی مقدار جدید F رو مشخص کنی ، با 5 نانوثانیه تاخیر این کار رو انجام بده .

1- 2- 3- 4- 5- 6- 7- 8- 9-

module Assign_Delay( input A, input B, output F ); assign #5 F = A & B; endmodule

البته تاخیر های فراوان دیگه ای هم داریم که من فقط بخشی از اونها رو در این جلسه بهتون گفتم. مثلا یک نوع تاخیر دیگه داریم که بین خطوط اعمال میشه و معمولا توی تست بنچ ها استفاده میشه ، به این صورت که مقدار یه سیگنال رو مثلا A=1 قرار میدیم و در خط بعدی مینویسیم #10; و سپس مینویسیم A=0 که این یعنی برای 10 نانوثانیه مقدار A یک باشه و سپس صفر بشه . دانلود فیلم جلسه

رفتن به جلسه بعد ...