1 - سطح گیت

جلسه اول (ماژول ها) جلسه دوم (گیت ها) جلسه سوم (نوع سیگنال) جلسه چهارم (پایان فصل)2 - مقداردهی مداوم

جلسه پنجم (اُپراتور ها) جلسه ششم (آرایه ها) جلسه هفتم (شرط ها) جلسه هشتم (فراخوانی ماژول) جلسه نهم (تست بنچ) جلسه دهم (نگاشت حافظه)3 - سطح رفتاری (ترکیبی)

جلسه یازدهم (بلاک Always) جلسه دوازدهم (ابزار ها) جلسه سیزدهم (نوع پردازش) جلسه چهاردهم (نکات تکمیلی) جلسه پانزدهم (پایان فصل)4 - سطح رفتاری (ترتیبی)

جلسه شانزدهم (لبه ها) جلسه هفدهم (تست بنچ 2) جلسه هجدهم (شمارنده ها) جلسه نوزدهم (ضرب و شیفت) جلسه بیستم (استیت ماشین) جلسه بیست و یکم (کشف رشته) جلسه بیست و دوم (فرکانس) جلسه بیست و سوم (نان بلاک) جلسه بیست و چهارم (پایان)5 - جلسات تمرینی

جلسه تمرین اول (تاخیر ها) جلسه تمرین دوم (الحاق-منطق) جلسه تمرین سوم (شیفت ها) جلسه تمرین چهارم (استیت)6 - مثال های پروژه محور

پروژه طراحی پردازنده RTL پروژه پردازنده Maano پروژه پردازنده MIPS7 - ارتباط و گفتگو

ارتباط با نویسنده گروه تلگرام تبلیغات و آگهیآموزش وریلاگ - جلسه 6 :

آموزش وریلاگ آموزش Verilog

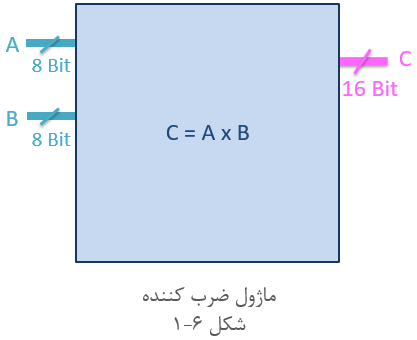

به عکس زیر دقت کنید ، یه ضرب کننده است :

دقت کردید تاحالا هرچی مدار کار کردیم ، سیگنال ها تک بیتی بود ؟ الان اگه بهمون بگن یه ضرب کننده بنویسید که دو عدد 8 بیتی رو درهم ضرب کنه ، چه باید کنیم ؟ هشت تا ضرب کننده یک بیتی بسازیم بهم وصل کنیم ؟ یک راه اینه اما مسئله اونقدرا هم پیچیده نیست ، چون داریم رفتاری مینویسیم فقط کافیه بگیم بجای ضربِ اعداد یک بیتی ، ضربِ اعداد هشت بیتی انجام بشه ، پس باید بلد باشیم سیگنال های چند بیتی رو تعریف کنیم که به اصطلاح بهشون میگیم بُردار یا آرایه که من اصلا این اسم هارو دوست ندارم ، آدم رو گُمراه می کنه ، بهترین اسم ، همون "چند بیتی" هست :

1- 2- 3- 4- 5- 6- 7- 8- 9-

module Mult8( input [7:0] A, input [7:0] B, output [15:0] C ); assign C = A * B; endmodule

در اینجا ورودی ها 8 بیتی و حاصلضرب 16 بیتی تعیین شد ( ضرب دو عدد 8 بیتی ، حاصل اش 16 بیت میشه ) ، نحوه تعیین کردن تعداد بیت ها بصورت [n-1:0] هست ، مثلا برای عدد هشت بیتی ، باید بگیم از بیتِ 0 تا بیتِ 7 که میشه هشت تا بیت. خب حالا بیاین جمع کننده جلسات قبلی رو ، این بار بصورت رفتاری بنویسیم :

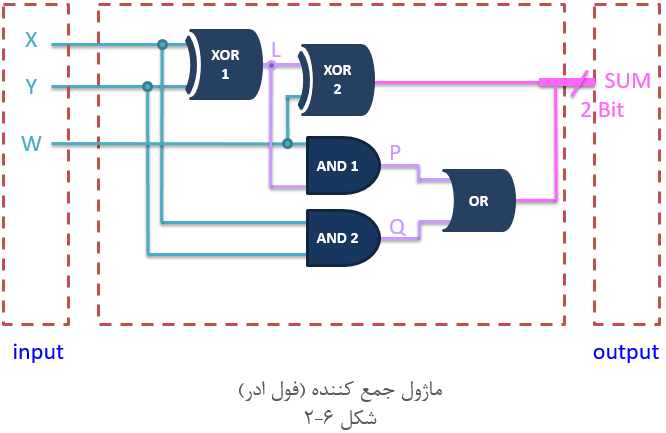

طبق شکل ، سه ورودی تک بیتی در نظر میگیریم و یک خروجی که دو بیتی هست (جمع سه عدد تک بیتی ، توی دو بیت جا میشه) :

1- 2- 3- 4- 5- 6- 7- 8- 9- 10-

module FullAdder( input X, input Y, input W, output [1:0] SUM ); assign SUM = X + Y + W; endmodule

به همین راحتی تموم شد ، حالا بیاین یه جمع کننده بنویسیم که دوتا عدد چهار بیتی رو باهم جمع میکنه (حاصل عدد پنج بیتی میشه )

1- 2- 3- 4- 5- 6- 7- 8- 9-

module FullAdder4( input [3:0] Num1, input [3:0] Num2, output [4:0] Result ); assign Result = Num1 + Num2; endmodule

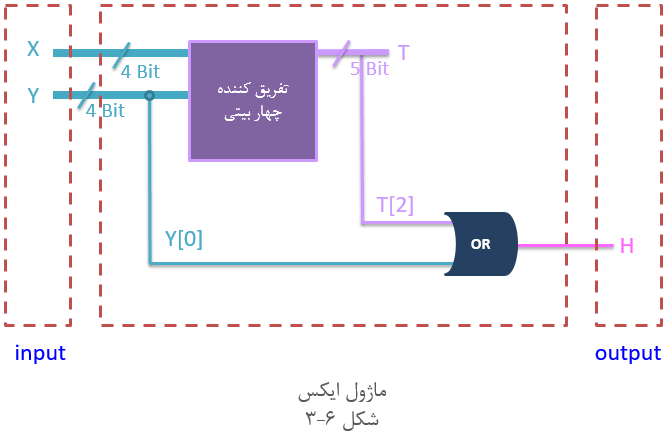

به شکل زیر نگاه کنید ، یه ماژول داریم که نمیدونیم دقیقا داره چیکار میکنه و از توصیف رفتار اون عاجزیم . البته میدونیم بخشی از مدار داره تفریق رو انجام میده و در ادامه اولین بیتِ Y با سومین بیتِ T اُر میشه (دقت کنید توی این مثال یه خروجی داریم به اسم H و سیگنال T سیگنال واسطه ای محسوب میشه) .

در اینطور مدارها ، میتونیم اون بخشی که رفتار شو میدونیم رو بصورت رفتاری بنویسیم و مابقی مدار رو با روش های دیگه مثل سطح گیت بنویسیم :

1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12- 13-

module UnKnown( input [3:0] X, input [3:0] Y, output H ); wire [4:0] T; assign T = X - Y; or(H,T[2],Y[0]); //Ya Mishe Nevesht: assign H=T[2]|Y[0]; endmodule

دیدیم که ما میتونیم سیگنال های واسطه ای رو هم به صورت چند بیتی تعریف کنیم و ازشون استفاده کنیم، همینطور برای استفاده از یک بیتِ خاص در یک سیگنال ، کافیه شماره بیتِ مورد نظر رو توی [ ] قرار بدیم .

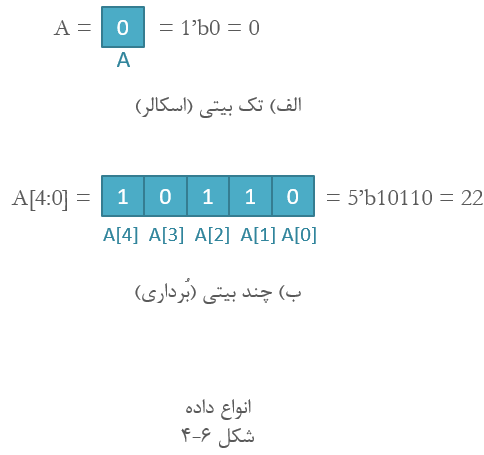

مثلا در شکل بالا چهارمین بیت از سیگنال 5 بیتی A ، میشه A[3] و اولین بیت میشه A[0] و آخرین بیت (پُر ارزشترین بیت) میشه A[4] . خب یادگرفتیم در یک ماژول میشه انواع روش هارو همزمان بکار گرفت، یعنی هم از گیت ها استفاده کنیم هم از روش های رفتاری. ترتیب اجرای کُد ها هم بصورت خط به خط نیست ، بلکه همزمان باهم اجرا می شوند و هیچ خطی نسبت به دیگری اولویت نداره ، این جلسه تموم شد . نکته : مبحث تاخیر هارو قرار بود توی این جلسه بگم اما به دلیل اینکه ممکنه این جلسه طولانی بشه ، توی بخش تمرین یک توضیح دادم ، بخش هایی که تحت عنوان تمرین بهتون معرفی میکنم اصلا چیز های اضافه نیست بلکه بسیار هم اصلی و اساسی هستش بنابراین به جلسه "تمرین (1)" برید و ببینید چطور میشه تاخیر هارو توی وریلاگ مدلسازی و تعریف کرد . دانلود فیلم جلسه

رفتن به جلسه بعد ...