1 - سطح گیت

جلسه اول (ماژول ها) جلسه دوم (گیت ها) جلسه سوم (نوع سیگنال) جلسه چهارم (پایان فصل)2 - مقداردهی مداوم

جلسه پنجم (اُپراتور ها) جلسه ششم (آرایه ها) جلسه هفتم (شرط ها) جلسه هشتم (فراخوانی ماژول) جلسه نهم (تست بنچ) جلسه دهم (نگاشت حافظه)3 - سطح رفتاری (ترکیبی)

جلسه یازدهم (بلاک Always) جلسه دوازدهم (ابزار ها) جلسه سیزدهم (نوع پردازش) جلسه چهاردهم (نکات تکمیلی) جلسه پانزدهم (پایان فصل)4 - سطح رفتاری (ترتیبی)

جلسه شانزدهم (لبه ها) جلسه هفدهم (تست بنچ 2) جلسه هجدهم (شمارنده ها) جلسه نوزدهم (ضرب و شیفت) جلسه بیستم (استیت ماشین) جلسه بیست و یکم (کشف رشته) جلسه بیست و دوم (فرکانس) جلسه بیست و سوم (نان بلاک) جلسه بیست و چهارم (پایان)5 - جلسات تمرینی

جلسه تمرین اول (تاخیر ها) جلسه تمرین دوم (الحاق-منطق) جلسه تمرین سوم (شیفت ها) جلسه تمرین چهارم (استیت)6 - مثال های پروژه محور

پروژه طراحی پردازنده RTL پروژه پردازنده Maano پروژه پردازنده MIPS7 - ارتباط و گفتگو

ارتباط با نویسنده گروه تلگرام تبلیغات و آگهیآموزش وریلاگ - جلسه 3 :

آموزش وریلاگ آموزش Verilog

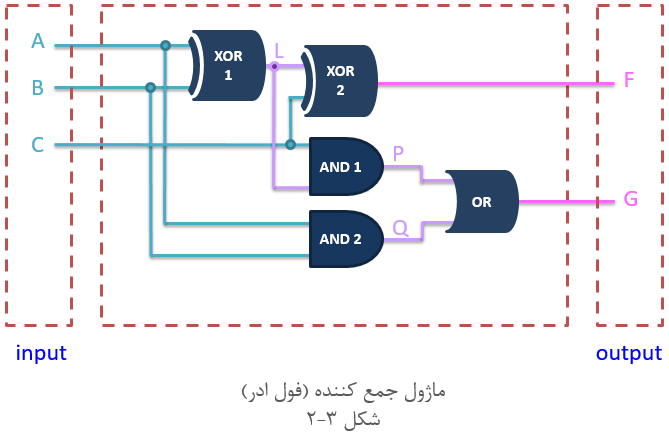

خب رفقا ، تا اینجا یاد گرفتیم هر مداری بهمون دادن کد وریلاگ شو بنویسیم . حالا بیاین یکم ریزتر به مسئله نگاه کنیم . ما توی مدار ها سیگنال های مختلفی داشتیم ، من میگم سیگنال ، شما میتونید بگید سیم ، متغییر یا هرچی . این سیگنال ها یا ورودی ماژول بودن ، یا خروجی ماژول بودن و یا سیگنال های واسطه بین گیت ها بودند . توی شکل زیر میتونیم سیگنال های ورودی ماژول رو آبی ، سیگنال های خروجی ماژول رو صورتی و سیگنال های واسطه ای رو بنفش ببینیم ، از این به بعد تمام شکل های ما با همین ترکیب رنگی خواهد بود ، یعنی ورودی ماژول آبی ، خروجی ماژول صورتی و سیگنال های واسطه بنفش .

حالا اینارو چرا گفتم ؟ ببینید ما تا الان نوع سیگنال هامون رو مشخص نکرده بودیم . سیگنال ها میتونن از نوع reg و یا wire باشن. اینکه اینها مفهوم شون چیه رو کاری نداشته باشید فقط به خاطر بسپارید که سیگنال های ما میتونن reg یا wire باشند . خب حالا از کجا بفهمیم یه سیگنال رو باید reg بذاریم یا wire ؟ بخاطر بسپارید که ورودی های ماژول اصلی ، همیشه باید از نوع wire باشند، اما خروجی های ماژول اصلی و سیگنال های واسطه ای طبق قوانین زیر : الف) اگر در برنامه از ساختار always استفاده کردیم ، آن سیگنالی که در always مقداردهی میشود باید reg تعریف شود و مابقی سیگنال ها مهم نیستن که reg باشند یا wire (به دلخواه خودتون هرچی خواستید بذارید) . ب) اگر در برنامه ساختار always نداشتیم ، همه سیگنال ها را wire تعریف میکنیم. ( اینکه always چیه رو بعدا میگم ) ج) اگر در برنامه ساختار assign داشتیم ، همه سیگنال های سمت چپِ تساوی ، باید wire باشند و مابقی سیگنال ها به دلخواه تون wire یا reg . ( اینکه assign چیه رو بعدا میگم ) خب ما تا اینجا میدونیم توی برنامه هامون از always و assign استفاده نکردیم ، پس توی قوانین بالا ، قانون ب رو باید رعایت کنیم و همه سیگنال های خروجی و واسطه ای رو wire تعریف کنیم . حالا سوال ، چرا توی جلسات قبلی اینکارو نکردیم ؟ چون وریلاگ یه خاصیت پیشفرض داره ، وقتی شما سیگنالی رو ، نوع شو مشخص نکنی ، خودش wire در نظر میگیره ، پس نوشتن wire ها الزامی نیست ، اما برنامه رو زیباتر میکنه. بیاین یه بار دیگه برنامه جلسه قبل رو بازنویسی کنیم و تمام سیگنال های موجود رو با کلید واژه wire بصورت wire تعریف کنیم :

1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12- 13- 14- 15- 16- 17- 18- 19- 20-

module FullAdder( input wire A, input wire B, input wire C, output wire F, output wire G ); wire L; wire P; wire Q; // wire L,P,Q; xor(L,A,B); xor(F,L,C); and(P,L,C); and(Q,A,B); or(G,P,Q); endmodule

از روی شکل زیر میتونید ببینید :

ورودی های ماژول تحت هر شرایطی wire تعریف میشن که شد ، مابقی سیگنال ها چون از always خبری نیست ، wire تعریف شدن . برای تعریف wire ها، هم میتونیم تک تک بنویسیم هم مثل خط 12 میتونیم همه رو توی یک خط بنویسیم . خب حالا بیاین یه قرارداد بین همدیگه داشته باشیم، از این جلسه به بعد من ورودی های اصلی ماژول رو wire تعریف نمی کنم تا وریلاگ خودش بصورت پیشفرض wire در نظر بگیره ، خروجی های ماژول رو هم اگه قرار بود wire باشن ، تعریف نمی کنم تا پیشفرض wire باشند . اما سیگنال های واسطه رو حتما wire تعریف میکنم ، با اینکه اجباری نیست اما اینکار باعث زیبایی برنامه خواهد شد . دانلود فیلم جلسه

رفتن به جلسه بعد ...