1 - سطح گیت

جلسه اول (ماژول ها) جلسه دوم (گیت ها) جلسه سوم (نوع سیگنال) جلسه چهارم (پایان فصل)2 - مقداردهی مداوم

جلسه پنجم (اُپراتور ها) جلسه ششم (آرایه ها) جلسه هفتم (شرط ها) جلسه هشتم (فراخوانی ماژول) جلسه نهم (تست بنچ) جلسه دهم (نگاشت حافظه)3 - سطح رفتاری (ترکیبی)

جلسه یازدهم (بلاک Always) جلسه دوازدهم (ابزار ها) جلسه سیزدهم (نوع پردازش) جلسه چهاردهم (نکات تکمیلی) جلسه پانزدهم (پایان فصل)4 - سطح رفتاری (ترتیبی)

جلسه شانزدهم (لبه ها) جلسه هفدهم (تست بنچ 2) جلسه هجدهم (شمارنده ها) جلسه نوزدهم (ضرب و شیفت) جلسه بیستم (استیت ماشین) جلسه بیست و یکم (کشف رشته) جلسه بیست و دوم (فرکانس) جلسه بیست و سوم (نان بلاک) جلسه بیست و چهارم (پایان)5 - جلسات تمرینی

جلسه تمرین اول (تاخیر ها) جلسه تمرین دوم (الحاق-منطق) جلسه تمرین سوم (شیفت ها) جلسه تمرین چهارم (استیت)6 - مثال های پروژه محور

پروژه طراحی پردازنده RTL پروژه پردازنده Maano پروژه پردازنده MIPS7 - ارتباط و گفتگو

ارتباط با نویسنده گروه تلگرام تبلیغات و آگهیآموزش وریلاگ - تمرین 4 :

آموزش وریلاگ آموزش Verilog

توی جلسه نوزدهم یه ضرب کننده نوشتیم ، اون موقع هنوز با استراتژی حل استیت ماشین ها آشنا نشده بودیم اما حالا که آشنا شدیم قصد دارم توی این جلسه تمرینی بهتون بگم چطور میشه با استراتژی استیت ماشین این ضرب کننده ترتیبی رو پیاده سازی کرد . اینکه استیت ماشین مون رو چطور رسم کنیم وحی منزل نیست ، هرکسی میتونه تعداد استیت ها و نحوه قرارگیری شون رو به سلیقه خودش و باتوجه به ماهیت مسئله رسم کنه .

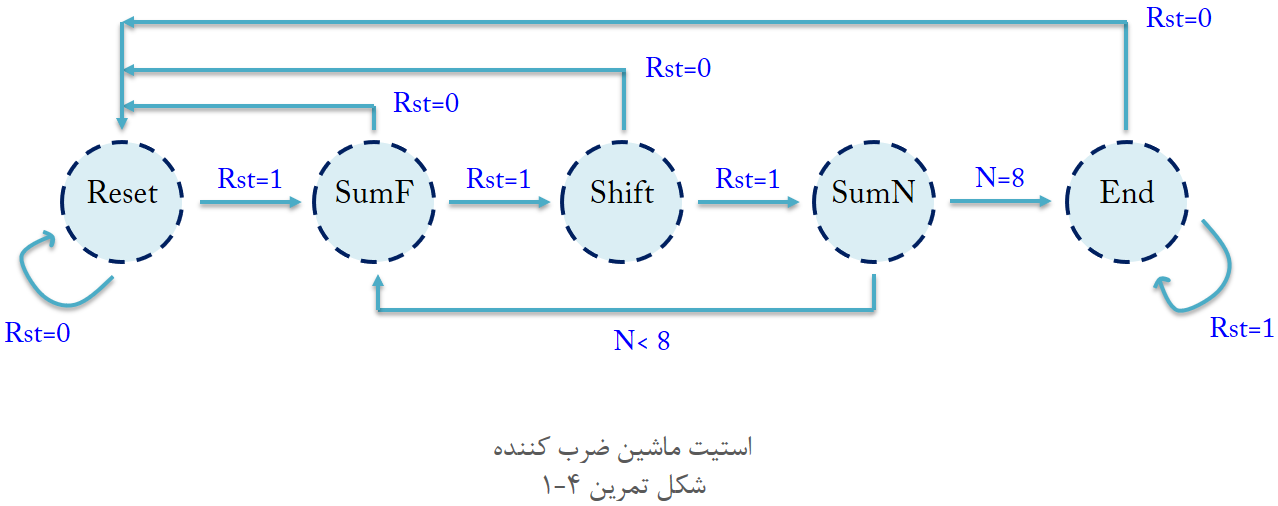

شکل بالا رو ببینید ، من از پنج استیت استفاده کردم ، استیت اول ریست هست و تا زمانی که سیگنال Rst من صفر باشه در همین استیت می مونیم . در صورتی که Rst یک بشه به استیت بعدی میریم که وظیفه داره یک شرط رو بررسی کنه (یک بودن کوچکترین بیتِ B) و در صورت برقراری شرط F=F+A رو انجام بده و سپس به استیت بعدی بره . در این استیت قراره A و B رو شیفت بعدی و بعدش به استیت بعدی بریم ، در این استیت یه واحد به N اضافه میکنیم و اگه حاصل از 8 کوچکتر شد به استیت SumF و درغیر اینصورت به استیت نهایی یعنی End خواهیم رفت . کد وریلاگ زیر برنامه این استیت ماشین هست البته زیاد جدی نگیرید تا خط 35 فقط تعاریف اولیه است و چیزی نداره ، از خط 35 تا 70 هم بخش اصلی برنامه است .

1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12- 13- 14- 15- 16- 17- 18- 19- 20- 21- 22- 23- 24- 25- 26- 27- 28- 29- 30- 31- 32- 33- 34- 35- 36- 37- 38- 39- 40- 41- 42- 43- 44- 45- 46- 47- 48- 49- 50- 51- 52- 53- 54- 55- 56- 57- 58- 59- 60- 61- 62- 63- 64- 65- 66- 67- 68- 69- 70- 71- 72- 73- 74- 75- 76- 77-

module Zarb_State( input Clk, input Rst, input [7:0] A, input [7:0] B, output reg [15:0] F, output reg DONE ); parameter Reset=3'b000; parameter SumF=3'b001; parameter Shift=3'b010; parameter SumN=3'b011; parameter End=3'b100; reg [15:0] Copy_A; reg [7:0] Copy_B; reg [7:0] N; reg [2:0] State; always @(posedge Clk or negedge Rst) begin if(~Rst) begin F=0; N=0; Copy_A={8'b0,A}; Copy_B=B; DONE=0; State=Reset; end else begin case(State) Reset : begin State=SumF; end SumF : begin if(Copy_B[0]) F=F+Copy_A; State=Shift; end Shift : begin Copy_A=Copy_A<<1; Copy_B=Copy_B>>1; State=SumN; end SumN : begin N=N+1; if(N==8) State=End; else State=SumF; end End : begin DONE=1; State=End; end endcase end end endmodule

تا خط 7 ورودی ها و خروجی هارو تعریف کردیم و خط 10 تا 14 به کمک پارامتر ها برای استیت هامون اسم انتخاب کردیم . خط 16 تا 19 هم متغییر های کمکی مون رو تعریف کردیم تا مقدار A , B و مقدار استیت و شمارنده N مون رو توشون ذخیره کنیم . ابتدا مشخص کردیم اگه سیگنال ریست فعال بود مقدار سیگنال هایی که تعریف کردیم چند باشه و همچنین استیت رو در حالت Reset قرار دادیم . در غیر اینصورت اگه سیگنال ریست فعال نبود با توجه به اینکه در چه استیتی هستیم ، مشخص کردیم به چه استیتی بریم و چه کارهایی انجام بشه .بنابراین یه کیس روی استیت زدیم و سپس مشخص کردیم که توی هر استیت چه اتفاقاتی رقم بخوره . (اگه مراحل ضرب کننده ترتیبی رو فراموش کردید به جلسه 19 مراجعه کنید).

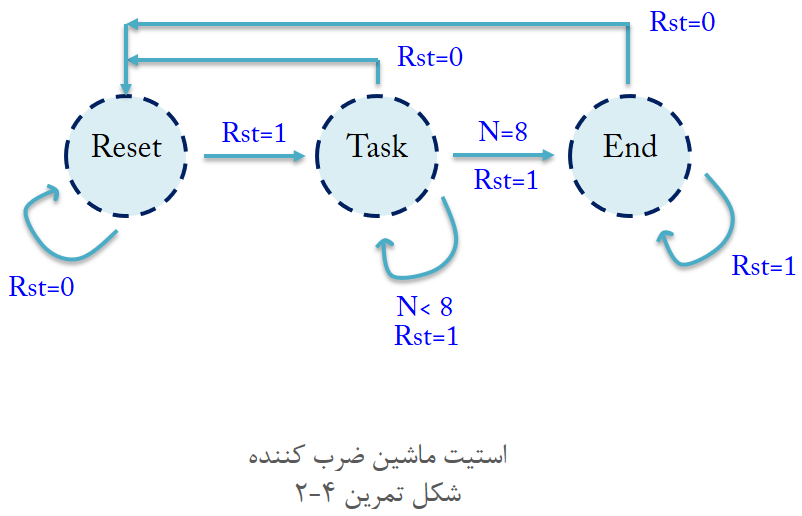

استیت ماشین بالا یک تعریف دیگه از ضرب کننده ترتیبی هست ، خواستم بهتون نشون بدم برای یک مسئله میشه چندین استیت ماشین رسم کرد و جواب ها یکتا نیست . در استیت ماشین بالا سه استیت داریم که در استیت اول ضرب کننده ریست هست ، در استیت بعدی عمل F=F+A و شیفت A ,B و اضافه شدن N همزمان انجام می شود و اگر N هشت شده بود به استیت انتهایی خواهیم رفت در غیر اینصورت در استیت Task باقی می مونیم و مجددا عمل جمع و شیفت رو انجام میدیم .

1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12- 13- 14- 15- 16- 17- 18- 19- 20- 21- 22- 23- 24- 25- 26- 27- 28- 29- 30- 31- 32- 33- 34- 35- 36- 37- 38- 39- 40- 41- 42- 43- 44- 45- 46- 47- 48- 49- 50- 51- 52- 53- 54- 55- 56- 57- 58- 59- 60- 61- 62- 63- 64- 65- 66- 67- 68-

module Zarb_State( input Clk, input Rst, input [7:0] A, input [7:0] B, output reg [15:0] F, output reg DONE ); parameter Reset=2'b00; parameter Task=2'b01; parameter End=2'b10; reg [15:0] Copy_A; reg [7:0] Copy_B; reg [7:0] N; reg [1:0] State; always @(posedge Clk or negedge Rst) begin if(~Rst) begin F=0; N=0; Copy_A={8'b0,A}; Copy_B=B; DONE=0; State=Reset; end else begin case(State) Reset : begin State=Task; end Task : begin if(Copy_B[0]) F=F+Copy_A; Copy_A=Copy_A<<1; Copy_B=Copy_B>>1; N=N+1; if (N==8) State=End; else State=Task; end End : begin DONE=1; State=End; end endcase end end endmodule

کد وریلاگ این استیت ماشین مشابه بخش قبلی است بنابراین من توضیح خاصی نمیدم و میذارم تماشاگر باشید . به یک نکته دقت کنید که توی جلسه 19 ، ضرب دو عدد 8 بیتی توی 8 کلاک انجام میشد در واقع توی هر یک کلاک ، عمل ضرب و جمع و افزودن N انجام میشد ، اما توی استیت ماشین اول انجام ضرب بیش از 25 کلاک طول خواهد کشید . چون برای هربار عمل جمع و شیفت باید سه استیت اجرا بشه و هر استیت نیاز به یک کلاک داره . البته توی استیت ماشین دومی که نوشتیم ، وضعیت بهتره و ضرب دو عدد نهایتا بین 8 تا 9 کلاک انجام میشه . حتی ما میتونستیم ضرب کننده رو بجای سه استیت ، توی یک استیت پیاده سازی کنیم اما ماهیت استراتژی استیت ماشین زیر سوال میره . هدف از استراتژی استیت ماشین این نیست که یک مسئله سریعتر عمل کنه ، بلکه هدف اینه یک مسئله به قسمت های ریز تر شکسته بشه تا از پیچیدگی اون کاسته بشه .

رفتن به جلسه بعد ...